RFSoC-based Trapped-Ion Qauntum Computer Control System

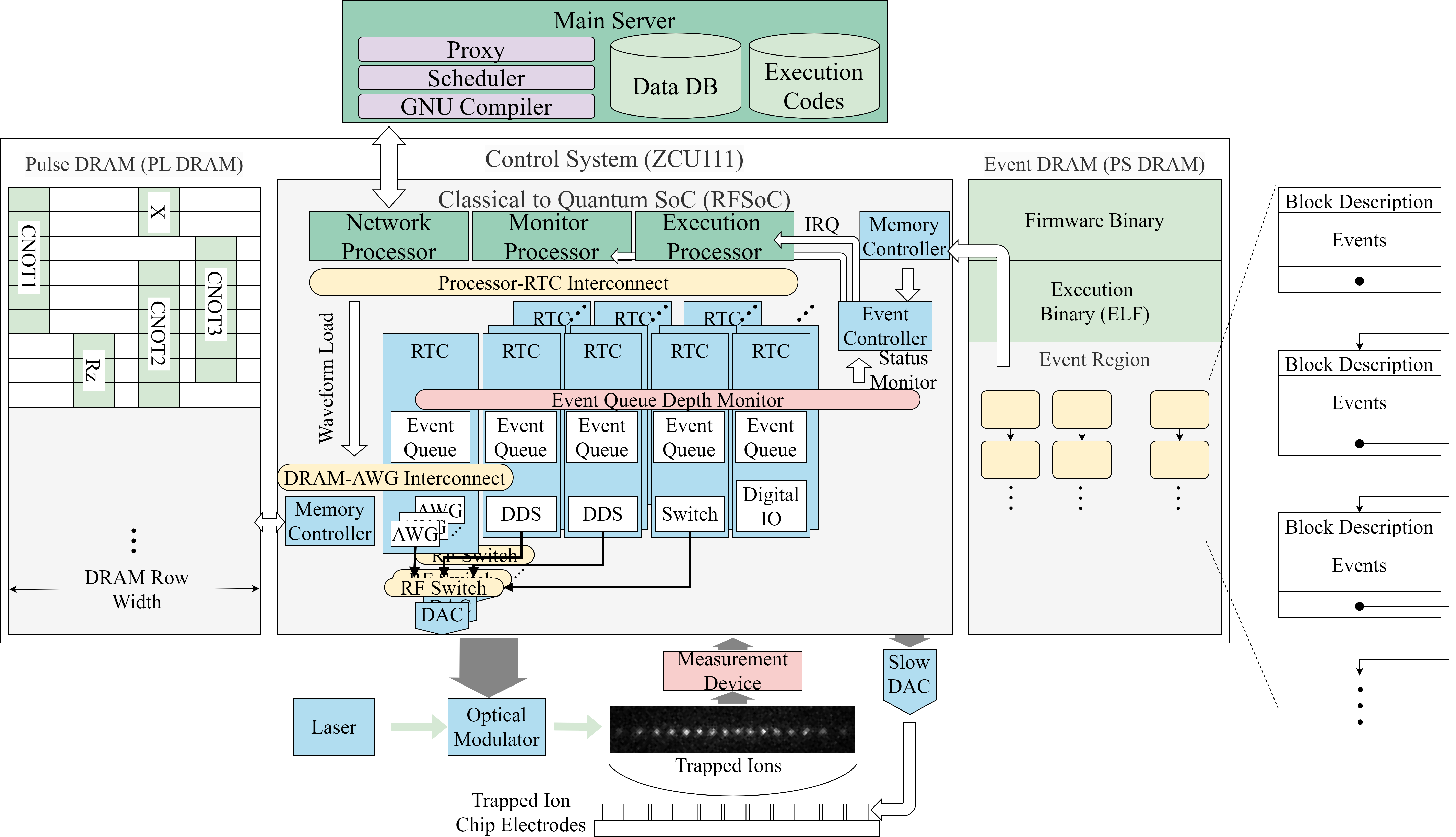

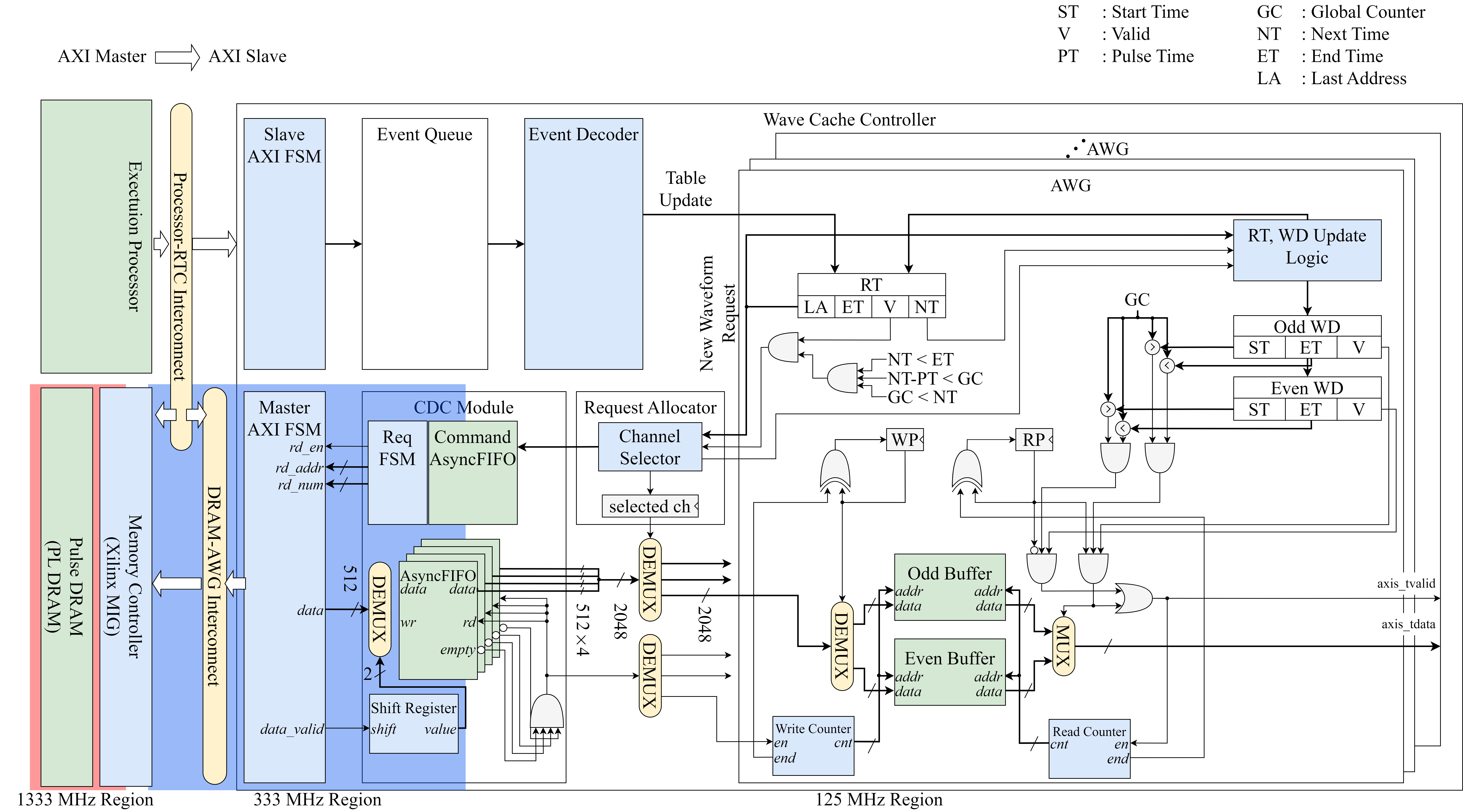

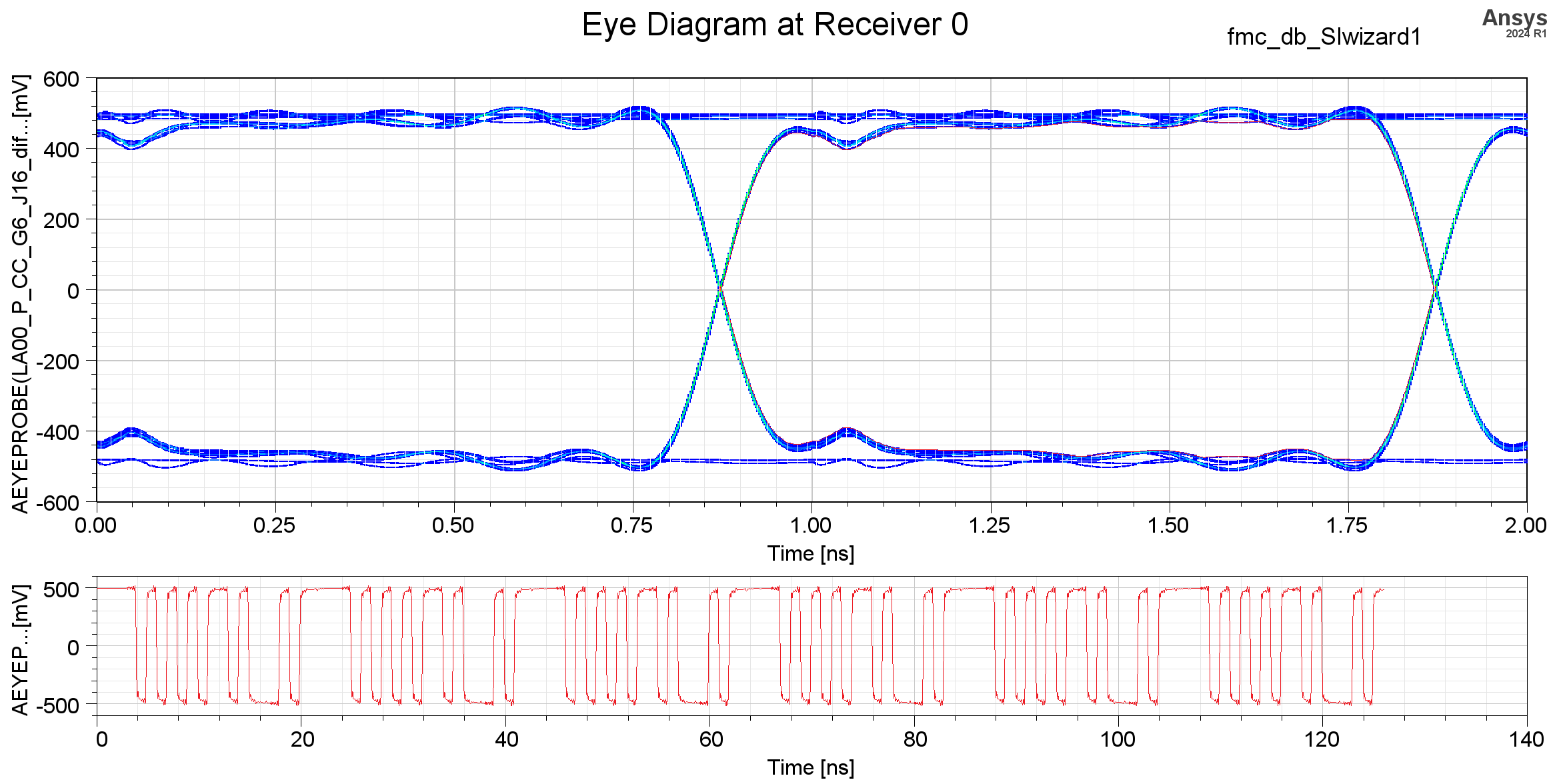

900 ns WCET latency with 1 channel, and 2.16 us with 8 channels, 4Gsamples, 1Gbps true-arb AWG with simultaneous ceaseless multi channel output with periodic DRAM refresh

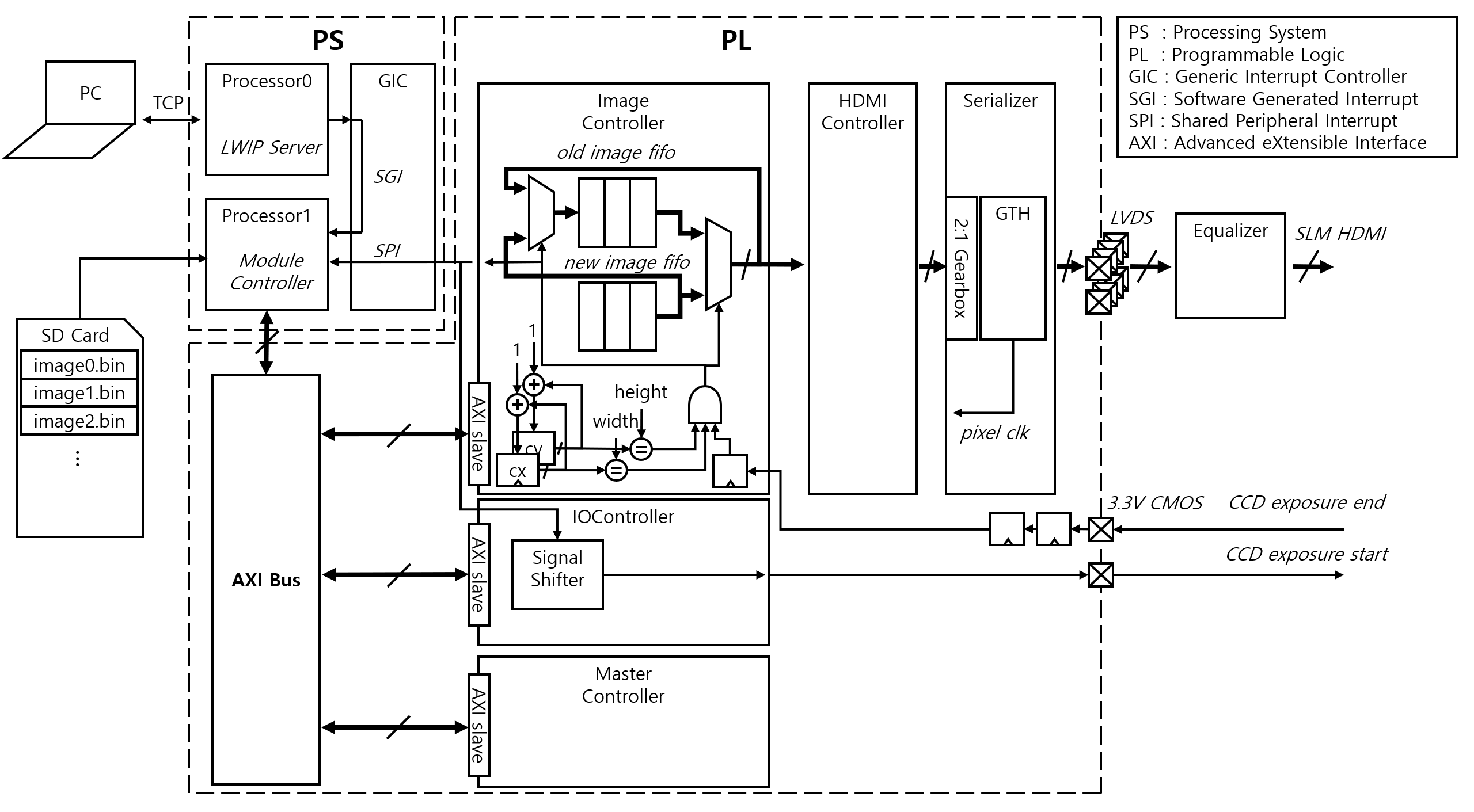

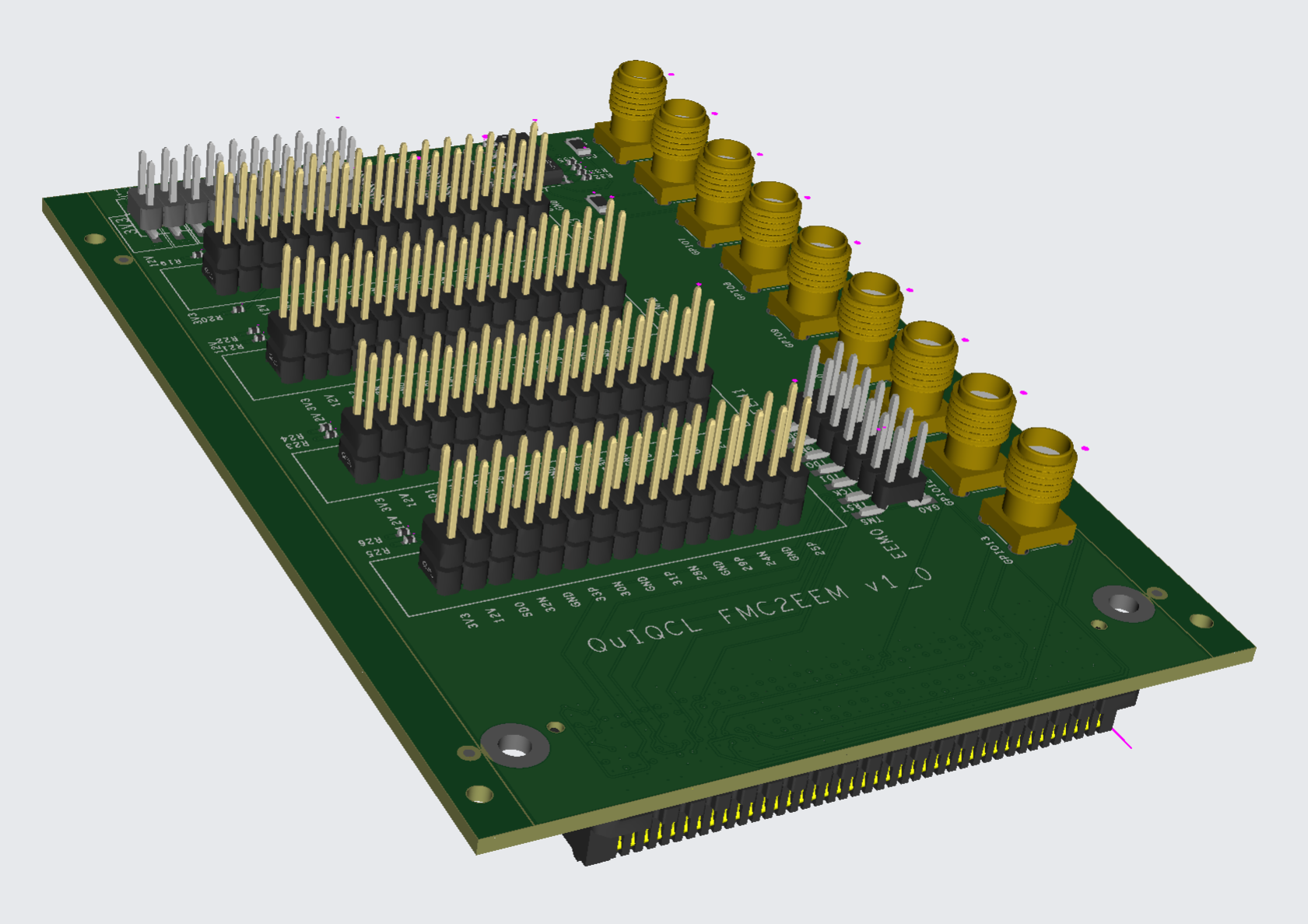

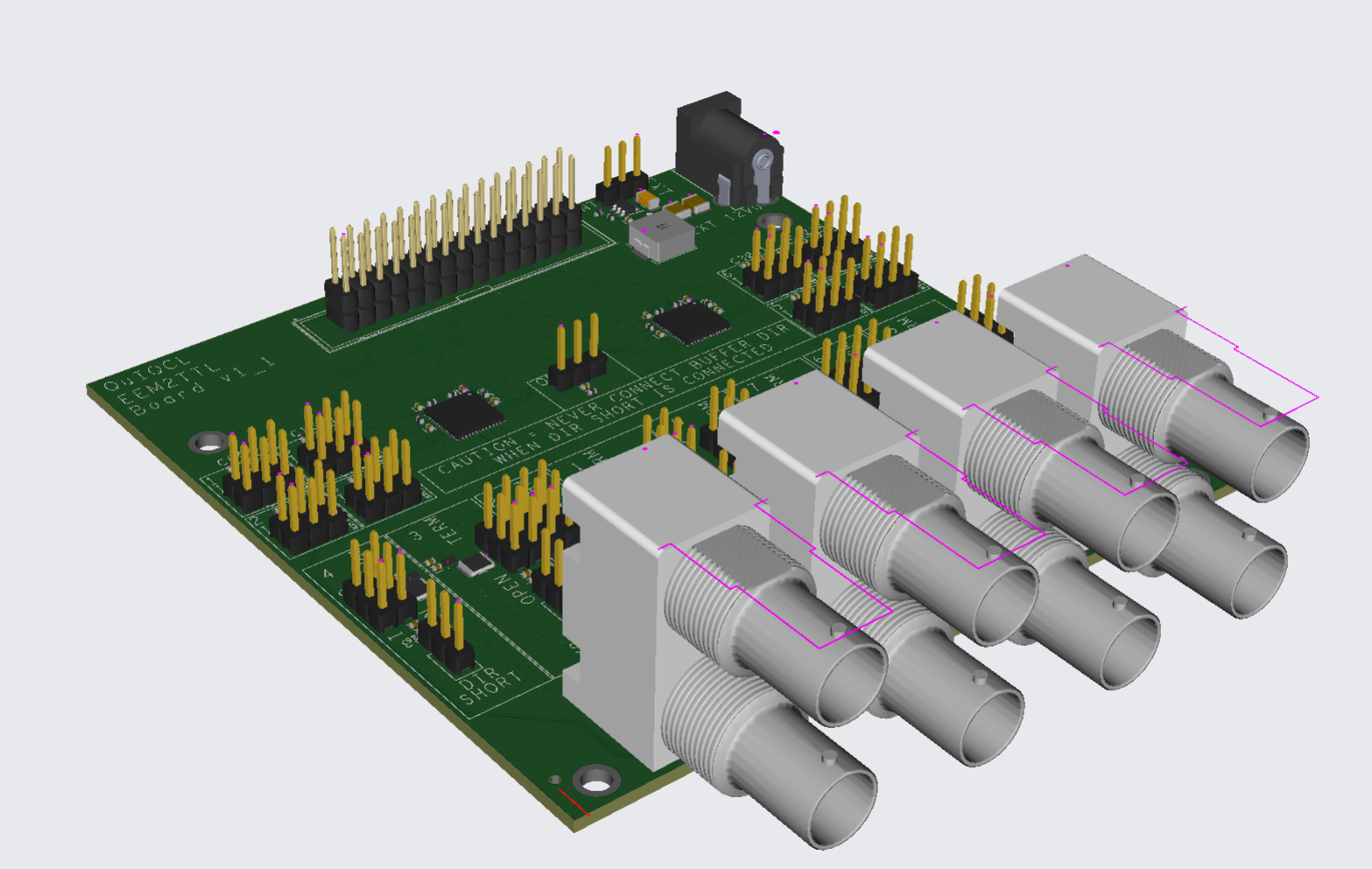

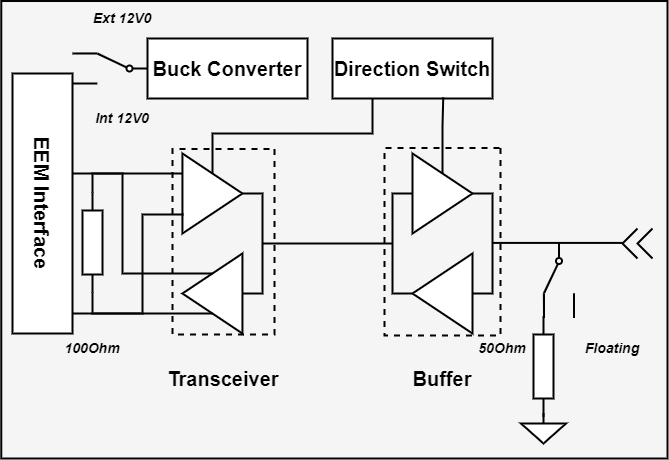

Non-blocking DMA achieving 3.2GBps with simultaneous multiple independent modules enabling 5192 electrodes control

Realtime shuttling, measurement, baremetal server running C++ code in field are integrated on single chip

Json meta file based automatic FPGA project generation tool chain

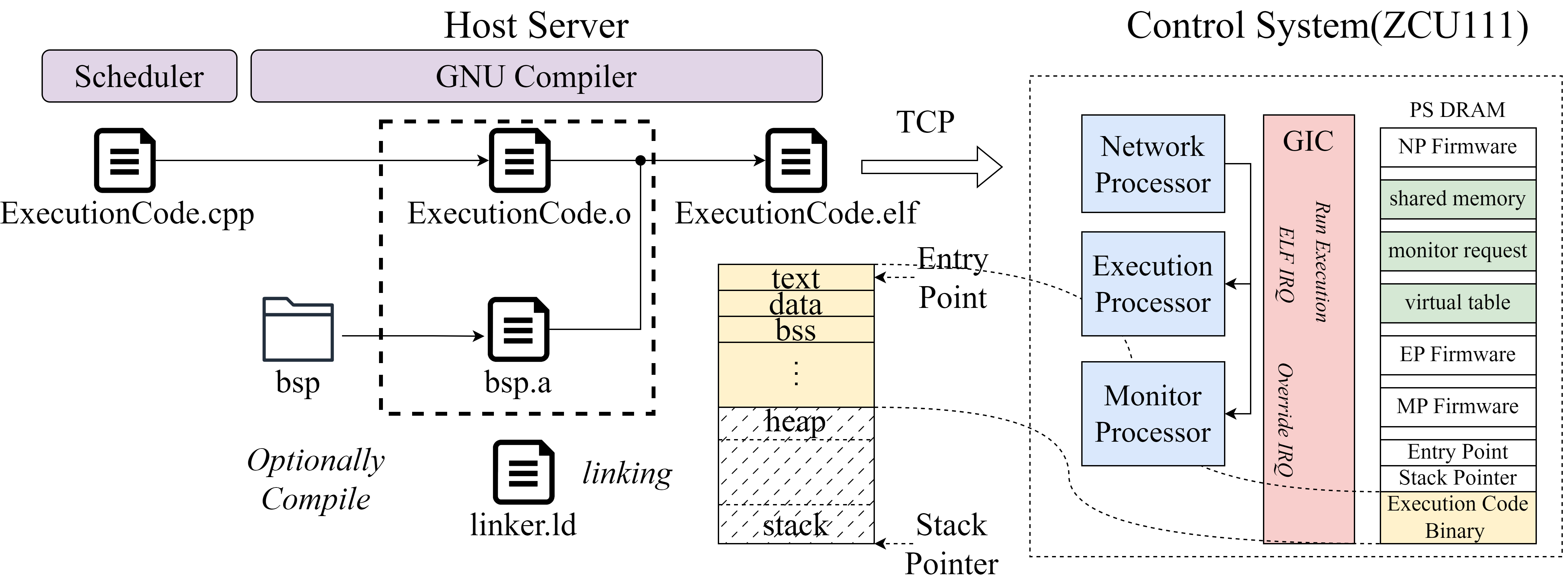

Compile and transmit binary code and schedule experiment request, and conduct RPC from FPGA

Pulse optimization through ADAM algorithm and is verified with experiment